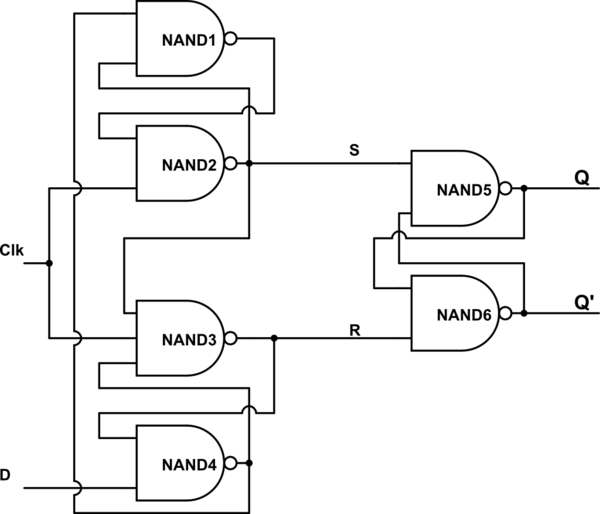

Positive Edge Triggered D Flip Flop Circuit Diagram

Let's analyze it for each clock edge. It is commonly used as a basic building block in digital. Timing diagram assume that q is initially zero for this problem. The positive edge d type flip flop, which changes its o/p according to the i/p with the +ve transition of the clock pulse.

Solved Question 1 Referring To The Positiveedge Triggered D

Then we study the timing diagram of the circuit in dsch and compare it with an ideal circuit timing diagram. Web in this paper, we investigate single electron encoded logic (seel) memory circuits, in which the boolean logic values are encoded as zero or one electron charges. Scan chains testing for latches to reduce area and.

Web Rising Edge Triggered D Flip Flop | Positive Edge D Flip Flop.

The output was initially zero (or to be precise, high impedance). This generated timing diagram is shown in.

Electronic How is the Truth Table of Positive edge triggered D Flip

praxe pilulka rytmus positive edge triggered d flip flop truth table

CircuitVerse A positiveedgetriggered D flipflop

Examples

Electronic CMOS implementation of D flipflop Valuable Tech Notes

Solved QUESTION 1 Referring to the positiveedge triggered D

PPT EENG 2710 Chapter 6 PowerPoint Presentation, free download ID

D positive edge triggered flip flop with t flip flop calgarylasopa